5.3.3 Оборудование для нейронных сетей: GPU, TPU, FPGA

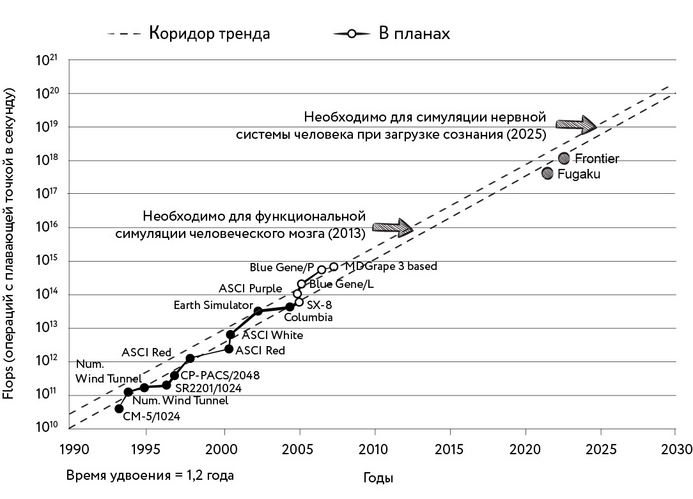

Но пока мы не достигли таких сияющих высот, не время пребывать в праздности, нужно искать пути дальнейшего развития. Брутто-быстродействие машин пока что растёт примерно теми же темпами, что и количество элементов интегральных схем. Если из написанной в 2005 г. книги Реймонда Курцвейла «Сингулярность близко» (The Singularity Is Near) взять график ожидаемого роста производительности вычислительных машин (на котором также приведена и оценка производительности, необходимой для симуляции работы человеческого мозга в реальном времени) и поместить на него точки, соответствующие двум самым быстрым суперкомпьютерам в мире на середину 2023 г., то они будут находиться почти внутри нарисованного Курцвейлом «коридора».

Пиковая производительность предыдущего лидера — компьютера, созданного при участии корпорации Fujitsu для использования в Центре вычислительных наук Института физико-химических исследований (яп. 理化学研究所 Rikagaku Kenkyūsho, сокращенно RIKEN, яп. 理研) и получившего название «Фугаку» (Fugaku), — достигает 537 Пфлопс, то есть 537 квадриллионов арифметических операций над числами с плавающей точкой в секунду. В тесте LINPACK производительность (Rmax) этой машины составляет 442 Пфлопс. «Фугаку» переместился на второе место рейтинга в мае 2022 г., когда в Ок-Риджской национальной лаборатории (Oak Ridge National Laboratory, ORNL) был запущен в эксплуатацию новый чемпион — суперкомпьютер Frontier (более официально Hewlett Packard Enterprise Frontier) или OLCF-5 (Oak Ridge Leadership Computing Facility, Ок-Риджская ведущая вычислительная установка) — первая машина, которая преодолела порог в один экзафлопс: пиковая производительность Frontier в тестах составила около 1,680 квинтиллиона операций с плавающей запятой в секунду (превысив прогнозное значение почти на 200 Пфлопс)[1], [2].

Рис. 114. Рост производительности суперкомпьютеров (логарифмическая шкала). Оригинальный рисунок из книги «Сингулярность близко» 2005 года, дополненный двумя новыми точками

Современные суперкомпьютеры состоят из множества вычислительных узлов, каждый из которых объединяет множество интегральных схем. И в отличие от аналогичных машин, создававшихся несколько десятилетий назад, эти схемы способны выполнять специфические операции, позволяющие более эффективно применять коннекционистские модели.

Такими схемами стали так называемые тензорные процессоры. Бум параллельных вычислений в 1980-е гг. совпал по времени с быстрым развитием технологий СБИС. Уже тогда исследователи осуществили первые опыты по созданию специализированных интегральных схем для искусственных нейронных сетей. Распространение сигнала в сети может быть описано в виде последовательных матричных операций: сложения, умножения, применения функции активации и так далее. Поэтому микросхема, реализующая такие операции на аппаратном уровне, может обеспечить существенный прирост скорости как при тренировке, так и при исполнении обученных нейронных сетей. Поскольку матричные операции в ряде случаев можно эффективно распараллелить (например, при сложении матриц суммирование элементов в различных областях можно осуществлять одновременно), можно добиться выполнения таких операций за гораздо меньшее число тактов, чем при последовательной обработке. Фактически речь идёт о многократном ускорении расчётов без замены элементной базы и технологии производства микросхем. Специализированные для решения тех или иных задач микросхемы сегодня принято называть интегральными схемами специального назначения (application-specific integrated circuit, ASIC).

Однако в 1980-е и 1990-е нейронные сети не были достаточно популярны, чтобы производители крупносерийных микросхем озаботились массовым выпуском ASIC’ов для нейросетевых моделей. К счастью, матричные операции оказались востребованы в области компьютерной графики — аппаратные графические ускорители, по сути дела, реализовывали изрядную долю необходимого набора инструкций. Ядра GPU изначально были предназначены для физических и графических вычислений, которые включают матричные операции.

В 2000-е и начале 2010-х видеокарты стали наиболее популярным видом оборудования, используемым для обучения искусственных нейронных сетей. По мере роста нейросетевых моделей производители GPU стали обращать больше внимания на нужды их разработчиков — архитектуры новых видеокарт учитывали требования, предъявляемые такими «нецелевыми» сценариями их применения. Более того, в середине 2010-х гг. стали появляться карты, для которых решение задач машинного обучения стало главной функцией устройства.

В мае 2016 г. компания Google представила устройство под названием Tensor processing unit (TPU) — тензорный процессор. Представители компании сообщили, что к этому моменту TPU уже использовался внутри дата-центров Google более года. Процессор был специально разработан для работы с фреймворком (программной платформой) Google TensorFlow, предназначенным для решения задач в области машинного обучения. В мае 2017 г. была выпущена вторая версия TPU, в мае 2018-го — третья, а в мае 2021-го — четвёртая[3].

Устройства от Google нельзя приобрести, но можно арендовать через облачные сервисы компании. Поэтому на текущий момент наиболее популярным оборудованием для обучения нейронных сетей остаются GPU от компании Nvidia, которая собирает на их основе специализированные серверы линейки DGX (в настоящее время свет увидели уже две версии таких машин). Участвуют в этой гонке и другие производители компьютерного «железа». Например, компания Intel в 2016 г. приобрела за 400 млн долларов стартап Nervana, в арсенале которого имеются два тензорных процессора: NNP-T (для обучения моделей, «T» в названии означает training) и NNP-I (для исполнения обученных моделей, «I» означает inferencing). В декабре 2019 г. Intel приобрёл ещё одну компанию, специализирующуюся на разработке TPU, ею стал израильский стартап Habana, в портфолио которого также содержатся два флагманских продукта: Habana Gaudi и Habana Goya. Сумма этой сделки составила уже 2 млрд долларов[4].

В настоящее время более ста компаний по всему миру создают интегральные схемы специального назначения (ASIC) и однокристальные системы (System-on-a-Chip, SoC), предназначенные для применения в области глубокого обучения. Некоторые из этих чипов просто умеют быстро умножать и складывать векторы и матрицы, другие (такие как, например, прототипы устройств от английского стартапа Graphcore) претендуют на более тонкий учёт специфики нейросетевых вычислений[5]. Американская компания Cerebras специализируется на изготовлении экспериментальных схем (язык не поворачивается сказать «микросхем») для тензорных вычислений размером с целую кремниевую пластину. Ещё в 2021 г. компания представила публике процессор под названием Wafer Scale Engine 2 (Машина масштаба кремниевой пластины 2, WSE-2), предназначенный для решения задач в области ИИ, выполненный на основе 7-нанометровой технологии и содержащий целых 2,6 трлн транзисторов и 850 000 вычислительных ядер[6]. Практически все крупные высокотехнологические компании имеют свои проекты подобных устройств. Помимо Google, Nvidia и Intel, в их число входят Facebook, Amazon (Inferentia), AMD, Tesla и многие другие[7].

Специализированные серверы, предназначенные для задач машинного обучения, обычно включают в себя несколько GPU или TPU, связанных специализированными быстрыми шинами для обмена данными. Например, сервер DGX-2 объединяет 16 GPU Tesla V100 и имеет суммарную заявленную производительность в 2 Пфлопс. Самый быстрый на данный момент российский суперкомпьютер «Кристофари», построенный Сбербанком совместно с Nvidia, включает в себя 75 узлов DGX-2, связанных сверхбыстрой шиной Infiniband. Именно скорость передачи данных между исполняющими ядрами и хранилищами данных является ахиллесовой пятой тензорных архитектур при решении ряда практических задач машинного обучения. Поэтому для GPU и TPU так важен объём оперативной памяти, доступной каждому из тензорных ядер. Выпустив свои тензорные процессоры третьей версии, компания Google удвоила объём памяти на одной плате TPU — с 64 до 128 GiB (в четвёртой версии предположительно увеличила до 256 GiB, однако на момент написания этих строк официальные данные ещё не были опубликованы). Но даже при таких объёмах обучение свёрточных нейронных сетей, предназначенных для обработки трёхмерных изображений или видео, — непростая задача. Обычно каждый GPU или TPU в таких случаях рассчитывает градиент параметров модели на небольшой порции данных, после чего полученные градиенты усредняются. При этом GPU/ TPU должны обменяться градиентами, а их размер при достаточно большом размере модели может быть весьма существенным.

Использование термина «тензорные процессоры» нередко вызывает нехилый баттхёрт у математиков, которые знают, что понятие тензора не эквивалентно понятию многомерного массива. Конечно, если вы не математик, то довольно удобно считать, что единичное число — это скаляр, одномерный массив — вектор, двумерный — матрица, а произвольный n-мерный массив — это тензор. Но всё-таки тензоры и многомерные массивы (они же многомерные таблицы) — это разные типы объектов. Тензор — это особый тип функции, а многомерный массив — структура данных, подходящая для представления тензора в системе координат, в таком случае отдельное число в таблице называют компонентом тензора. Математики обычно определяют тензор как полилинейную функцию, то есть функцию нескольких векторных переменных, которая линейна по каждому из аргументов. Тензор линейно преобразует элементы одного линейного пространства в элементы другого, что бы это ни значило. Частными случаями тензоров являются скаляры, векторы, билинейные формы и так далее. Число измерений таблицы, представляющей тензор, называют его валентностью или рангом тензора. Это была минутка полезных математических знаний.

«„Тензоры“ в TensorFlow не имеют ничего общего с тензорами! — пишет рассерженный пользователь Locken Lui в комментарии к посту на платформе Medium. — Это злоупотребление использованием термина тензор. „Тензоры“ в смысле, используемом в TensorFlow, являются просто многомерными матрицами и не имеют ничего (!) общего с реальными тензорами в физике, континуальных теориях или теориях поля. Вы смешиваете эти понятия в своём посте. Возможно, название „Tensor“ было выбрано потому, что оно звучит проще, чем “MultidimensionalMatrixFlow”»[8]. Мы понимаем вашу боль, Locken Lui, и разделяем её.

В последние годы производители электроники уделяют большое внимание созданию так называемых граничных [edge] устройств. Под граничными вычислениями [edge computing] обычно понимают децентрализованную обработку данных, при которой вычисления производятся на «последней миле» компьютерной сети. Вычислительные процедуры, производящие объёмный и в то же время индивидуализированный пользовательский контент, в ряде случаев выгодно располагать ближе к точке его потребления. Поэтому возникает необходимость в устройствах, способных выполнять необходимые вычисления в составе мобильных устройств, систем «умных домов», узлов игрового стриминга [edgelets] и так далее.

В июле 2018 г. Google анонсировала Edge TPU — специализированную микросхему ASIC, предназначенную для запуска моделей машинного обучения для граничных вычислений. Edge TPU имеет значительно меньший размер и потребляет гораздо меньше энергии по сравнению с облачными TPU.

Смешная третья опция для современного проектировщика нейронных сетей (помимо GPU/TPU и CPU, обычных центральных процессоров, которые, кстати сказать, сегодня тоже активно развиваются в направлении расширения наборов инструкций за счёт быстрых векторных операций) — это использование FPGA — устройств, относящихся к категории программируемых логических интегральных схем (ПЛИС). FPGA в наши дни часто используют для прототипирования ASIC: удобно сперва испытать ту или иную архитектуру микросхемы, прежде чем отправить её в серийное производство.

Если вас интересует более подробный анализ состояния дел в мире оборудования, предназначенного для задач глубокого обучения, то рекомендую регулярно дополняемый обзор[9] от Григория Сапунова, в котором можно найти сведения о последних проектах в чудесном мире CPU, GPU и TPU, ПЛИС и ASIC.

- ↑ Schneider D. (2021). Frontier supercomputer to usher in exascale computing / IEEE Spectrum, 23 Dec 2021 // https://spectrum.ieee.org/exascale-supercomputing

- ↑ TOP500 Release (2023). June 2023 / TOP500 The List // https://www.top500.org/lists/top500/2023/06/

- ↑ Weiss T. R. (2021). Google Launches TPU v4 AI Chips / HPC wire, May 20, 2021 // https://www.hpcwire.com/2021/05/20/google-launches-tpu-v4-ai-chips/

- ↑ Mayersen I. (2020). Intel is sacrificing previous AI acquisitions for Habana: They've traded one AI startup for another / TechSpot, February 2, 2020 // https://www.techspot.com/news/83826-intel-sacrificing-their-previous-ai-acquisitions-habana.html

- ↑ Toon N. (2020). Introducing 2nd generation IPU systems for AI at scale // https://www.graphcore.ai/posts/introducing-second-generation-ipu-systems-for-ai-at-scale

- ↑ Cerebras Systems Smashes the 2.5 Trillion Transistor Mark with New Second Generation Wafer Scale Engine (2021) // https://www.cerebras.net/press-release/cerebras-systems-smashes-the-2-5-trillion-transistor-mark-with-new-second-generation-wafer-scale-engine/

- ↑ Suryavansh M. (2019). How to make your own deep learning accelerator chip! / Towards Data Science, Sep 18, 2019 // https://towardsdatascience.com/how-to-make-your-own-deep-learning-accelerator-chip-1ff69b78ece4

- ↑ Locken Lui (2018). “Tensors” in TensorFlow… / Medium, Aug 24, 2018 // https://medium.com/@lockenluy/tensors-in-tensorflow-have-nothing-to-do-with-tensors-2ffb75172d05

- ↑ Sapunov G. (2021). Hardware for Deep Learning / Intento, Feb 26, 2018 — Jan, 11, 2021 // https://blog.inten.to/hardware-for-deep-learning-current-state-and-trends-51c01ebbb6dc